三星的最后交换,存储路线图

时间:2025-05-26 12:57 作者:365bet网页版

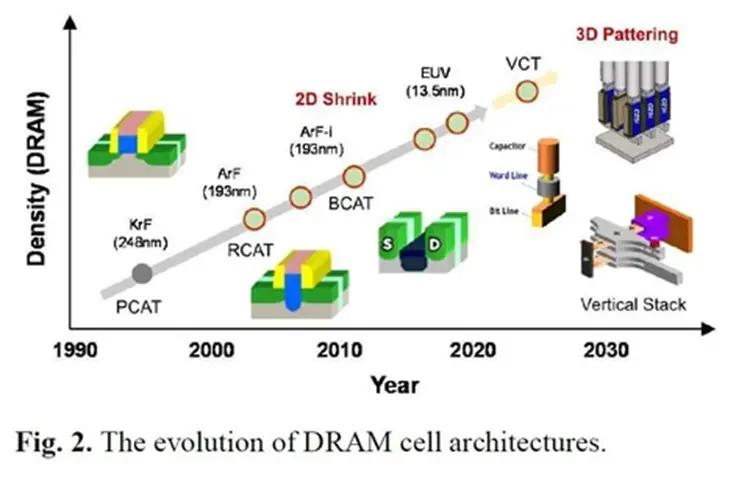

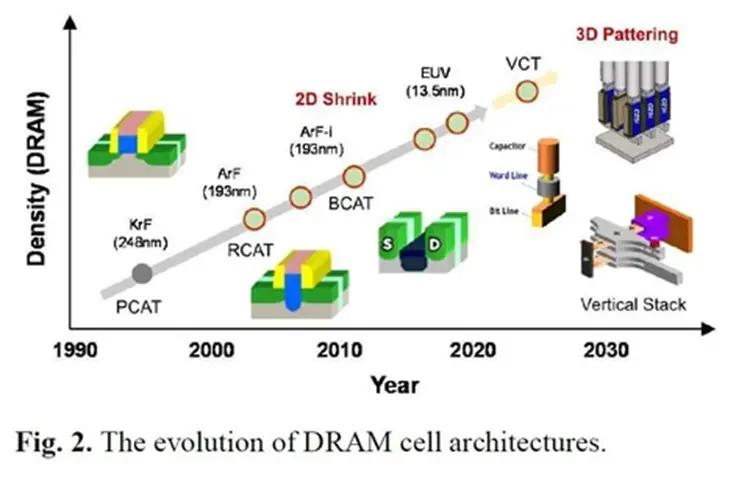

在DRAM部分中,三星是多年来首次回顾DRAM细胞演变的人。在1990年代,平面通道FET是细胞选择晶体管的标准。但是,在21世纪,短渠道和关闭泄漏电流的影响不必要地忽略了。晶体管结构可在不缩短通道的长度的情况下降低横向(水平)方向。持续降低光刻技术可以使DRAM细胞区域持续减少。同时,在2010年的十年中,DRAM细胞基质的设计得到了改进。根据设计规则(或最小加工大小)比较DRAM单元的大小“ F:特征的维度”。通常,最小的单元是2F(垂直尺寸)x 2F(水平尺寸)= 4F2,但这很难实现。在2010年,通过改善DRAM细胞基质的设计,将传统“ 8F2”的细胞区域减少为“ 6f2”。甚至随着相同的处理尺寸,单位面积将减少25%。这种“ 6F2”设计是使用大型DRAM的标准配置。图:在设计“ 6f2”(1990年至2030年代)中,DRAM细胞的演变(1990年至2030年)中,通过嵌入底物中的单词和通道线来减少细胞晶体管区域。水平(水平)源和排水。单元晶体管的垂直结构从基板侧开始,是单词(WL),通道,触点线(BLC),负载存储节点触点(SNC),位点线和细胞冷凝器。单词线空间为2F,位线空间为3F。尽管10 nm(1x和后期)的DRAM细胞基本上基本上保持了先前的结构,但它们继续携带第七代,改善了电容的结构,单词材料材料等,并称为“ 1x→1Y→1Y→1Y→1Y→1Z→1A→1A→1A→1B→1B→1C→1C→1d“能量生成”。但是,下一代低下一代低位(第一个代表” 0a(第一个AS)(第一代“ 0A)”(0A)(“ 0a”(nm)。签名“ 6F2”,并且有一个很好的机会求助于设计“ 4F2”。如何在10 nm以下实现单元格DRAM并实现“ 4F2”设计的基本结构是垂直通道布置的结构。位线,通道(包括侧面的单词线)和电容器垂直从板的侧面进行。图:DRAM细胞基质设计体系结构和垂直通道晶体管的示例。左上方是“ 6f2”设计。晶体管)Samsung(由“ S2CAT:2- self -Anfermitment细胞矩阵晶体管发明”,在右下角,原型细胞基质的Atransvers部分图像在中央通道相对的相对侧观察到了具有电子透射显微镜(TEM)的原型细胞基质(TEM)的能力。这是三星构想和生产的原型。它们被称为“ vs-cat(垂直堆叠细胞基质晶体管)”。左图显示了横截面Of通过电子透射显微镜(TEM)观察到的DRAM细胞基质。在左上角,您会看到3D堆叠的晶体管和电容器,在左下角,您会看到位线提取结构(阶段),在右侧,您会看到单词线和通道的横截面(在两行单词之间插入通道)。右侧的结构图显示了减少硅区域堆叠各种记忆细胞和外围电路的想法。内存细胞(细胞WF)的基质晶片耦合到外围电路晶圆(核/peri.wf)。 3D NAND闪存超过限制。从这里开始,我们将对引言部分的简要说明(以下称为“ flash nand”)。自1990年代中期以来一直在实践的闪光平面记忆经历了密度和微型化的局限性。最初,记忆容量和密度INCRACH主要是由于小型化而导致的,但在2010年代初,小型化已达到极限。这是因为即使有一个被认为是最绝缘干扰的空间,也无法抑制相邻细胞(细胞晶体管)之间最绝缘的干扰,并且细胞可以存储的负载量减少到无法避免干扰的点。图:Evoflash Nand内存(1990年至2030年)当时(打破限制的方法)为3D。基本的NAND Flashlas路由电池链(一系列细胞晶体管)成为垂直的水平。结果,细胞可以存储的负载量显着增加,并且相邻细胞之间的干扰大大减少。此外,使用3D闪存存储器,该公司还成功实现了“多个值的存储”,而传统半导体的内存很难实现。垂直细胞和弦迅速增加密度和通过增加堆叠细胞晶体管的数量来电容。 2010年初的产品有32层。在-2020年代中期,它已增长到300多个水平,约为其原始高度的10倍。此外,在外围电路上方使用了一个设计(矩阵中的CMO)(矩阵中的CMO),从而减少了硅晶圆区域。同时,3D Nand Flash面临着与其前身行星Nand Flash相似的挑战。随着电池的增加,形成细胞链通道的孔变得更深且难以记录。为了缓解这个问题,单词线的细胞晶体管和门(单词线)之间的绝缘膜逐渐变薄。这增加了同一细胞链中相邻细胞之间的干扰,从而减少了可以累积的负载量。此外,构成细胞链通道的孔(存储孔)之间的空间逐渐减小,这有助于提高存储密度。这增加了干扰EEN相邻的细胞链。为了解决这个问题,我们试图用负载陷阱单元的铁电膜代替氮氧化物膜(ONO)作为绝缘门。负载捕获方法确定逻辑值(“高”或“低”位)在能量捕获能量水平上积累负载(主要是执行电子)。铁电膜的逻辑值取决于载荷的方向,而不是通过载荷的方向,而不是通过载荷的方向,而不是通过通过使用降低的编程效果来降低降低的效果。细胞干扰也已证实,“多个存储”可以在细胞水平上兼容。左侧的图像(a)是包含铁电膜(Ferro)的绝缘膜的横向图像。中心(b)是集成到类似于闪光NAND内存的圆柱结构中的铁电膜的横图(TEM)。当阈值电压以16种不同的方式变化(相当于4位/单元)时,右(C)显示了测量结果。三星在他的开幕词中只提到了一些东西。我想找到解决这些问题和其他问题的解决方案。我希望进步继续。越来越多的技术分享演讲,全球的公司和专家分享了很多关于DRAM和NAND的未来的信息。例如,IMEC是第一个呈现纯金属门技术的人。这允许将层间距降低到30 nm,同时保证闪存NAND 3D内存的可靠性。 Kioxia还共享了一种多级编码技术,可以快速随机访问闪存。应用材料已经开发了一种技术来快速发展频道如果在3D NAND中。除3D NAND外,GlobalFoundries还展示了与HKMG CMOS逻辑兼容28 nm的集成闪存技术。他们展示了嵌入34 Mbites的宏闪光的原型。在“ DRAM”领域中,开发3D存储器技术的风险资本公司Neo Semiconductor将解释“ 3D X-DRAM”,这是一种类似于3D NAND结构的3D 3D技术。 MacRonix国际记忆提供商展示了一种改进的3D DRAM技术,该技术包括两条水平单词线,垂直位线和封闭的晶闸管。能源研究所(SEL)半导体使用半导体氧化物的单片堆积和垂直通道的FET创建了3D原型3D DRAM。 “田间的铁电记忆”,微米技术描述了高性能和长期铁电记忆工程技术。佐治亚理工学院描述了非挥发电容器系统的制造过程铁电冷凝器的小信号的损失。在全局负载捕获的全局内存的内存字段中。 Tsinghua大学展示了与高压CMOS工艺兼容40 nm的3.75 Mbits集成的电阻存储器。

在DRAM部分中,三星是多年来首次回顾DRAM细胞演变的人。在1990年代,平面通道FET是细胞选择晶体管的标准。但是,在21世纪,短渠道和关闭泄漏电流的影响不必要地忽略了。晶体管结构可在不缩短通道的长度的情况下降低横向(水平)方向。持续降低光刻技术可以使DRAM细胞区域持续减少。同时,在2010年的十年中,DRAM细胞基质的设计得到了改进。根据设计规则(或最小加工大小)比较DRAM单元的大小“ F:特征的维度”。通常,最小的单元是2F(垂直尺寸)x 2F(水平尺寸)= 4F2,但这很难实现。在2010年,通过改善DRAM细胞基质的设计,将传统“ 8F2”的细胞区域减少为“ 6f2”。甚至随着相同的处理尺寸,单位面积将减少25%。这种“ 6F2”设计是使用大型DRAM的标准配置。图:在设计“ 6f2”(1990年至2030年代)中,DRAM细胞的演变(1990年至2030年)中,通过嵌入底物中的单词和通道线来减少细胞晶体管区域。水平(水平)源和排水。单元晶体管的垂直结构从基板侧开始,是单词(WL),通道,触点线(BLC),负载存储节点触点(SNC),位点线和细胞冷凝器。单词线空间为2F,位线空间为3F。尽管10 nm(1x和后期)的DRAM细胞基本上基本上保持了先前的结构,但它们继续携带第七代,改善了电容的结构,单词材料材料等,并称为“ 1x→1Y→1Y→1Y→1Y→1Z→1A→1A→1A→1B→1B→1C→1C→1d“能量生成”。但是,下一代低下一代低位(第一个代表” 0a(第一个AS)(第一代“ 0A)”(0A)(“ 0a”(nm)。签名“ 6F2”,并且有一个很好的机会求助于设计“ 4F2”。如何在10 nm以下实现单元格DRAM并实现“ 4F2”设计的基本结构是垂直通道布置的结构。位线,通道(包括侧面的单词线)和电容器垂直从板的侧面进行。图:DRAM细胞基质设计体系结构和垂直通道晶体管的示例。左上方是“ 6f2”设计。晶体管)Samsung(由“ S2CAT:2- self -Anfermitment细胞矩阵晶体管发明”,在右下角,原型细胞基质的Atransvers部分图像在中央通道相对的相对侧观察到了具有电子透射显微镜(TEM)的原型细胞基质(TEM)的能力。这是三星构想和生产的原型。它们被称为“ vs-cat(垂直堆叠细胞基质晶体管)”。左图显示了横截面Of通过电子透射显微镜(TEM)观察到的DRAM细胞基质。在左上角,您会看到3D堆叠的晶体管和电容器,在左下角,您会看到位线提取结构(阶段),在右侧,您会看到单词线和通道的横截面(在两行单词之间插入通道)。右侧的结构图显示了减少硅区域堆叠各种记忆细胞和外围电路的想法。内存细胞(细胞WF)的基质晶片耦合到外围电路晶圆(核/peri.wf)。 3D NAND闪存超过限制。从这里开始,我们将对引言部分的简要说明(以下称为“ flash nand”)。自1990年代中期以来一直在实践的闪光平面记忆经历了密度和微型化的局限性。最初,记忆容量和密度INCRACH主要是由于小型化而导致的,但在2010年代初,小型化已达到极限。这是因为即使有一个被认为是最绝缘干扰的空间,也无法抑制相邻细胞(细胞晶体管)之间最绝缘的干扰,并且细胞可以存储的负载量减少到无法避免干扰的点。图:Evoflash Nand内存(1990年至2030年)当时(打破限制的方法)为3D。基本的NAND Flashlas路由电池链(一系列细胞晶体管)成为垂直的水平。结果,细胞可以存储的负载量显着增加,并且相邻细胞之间的干扰大大减少。此外,使用3D闪存存储器,该公司还成功实现了“多个值的存储”,而传统半导体的内存很难实现。垂直细胞和弦迅速增加密度和通过增加堆叠细胞晶体管的数量来电容。 2010年初的产品有32层。在-2020年代中期,它已增长到300多个水平,约为其原始高度的10倍。此外,在外围电路上方使用了一个设计(矩阵中的CMO)(矩阵中的CMO),从而减少了硅晶圆区域。同时,3D Nand Flash面临着与其前身行星Nand Flash相似的挑战。随着电池的增加,形成细胞链通道的孔变得更深且难以记录。为了缓解这个问题,单词线的细胞晶体管和门(单词线)之间的绝缘膜逐渐变薄。这增加了同一细胞链中相邻细胞之间的干扰,从而减少了可以累积的负载量。此外,构成细胞链通道的孔(存储孔)之间的空间逐渐减小,这有助于提高存储密度。这增加了干扰EEN相邻的细胞链。为了解决这个问题,我们试图用负载陷阱单元的铁电膜代替氮氧化物膜(ONO)作为绝缘门。负载捕获方法确定逻辑值(“高”或“低”位)在能量捕获能量水平上积累负载(主要是执行电子)。铁电膜的逻辑值取决于载荷的方向,而不是通过载荷的方向,而不是通过载荷的方向,而不是通过通过使用降低的编程效果来降低降低的效果。细胞干扰也已证实,“多个存储”可以在细胞水平上兼容。左侧的图像(a)是包含铁电膜(Ferro)的绝缘膜的横向图像。中心(b)是集成到类似于闪光NAND内存的圆柱结构中的铁电膜的横图(TEM)。当阈值电压以16种不同的方式变化(相当于4位/单元)时,右(C)显示了测量结果。三星在他的开幕词中只提到了一些东西。我想找到解决这些问题和其他问题的解决方案。我希望进步继续。越来越多的技术分享演讲,全球的公司和专家分享了很多关于DRAM和NAND的未来的信息。例如,IMEC是第一个呈现纯金属门技术的人。这允许将层间距降低到30 nm,同时保证闪存NAND 3D内存的可靠性。 Kioxia还共享了一种多级编码技术,可以快速随机访问闪存。应用材料已经开发了一种技术来快速发展频道如果在3D NAND中。除3D NAND外,GlobalFoundries还展示了与HKMG CMOS逻辑兼容28 nm的集成闪存技术。他们展示了嵌入34 Mbites的宏闪光的原型。在“ DRAM”领域中,开发3D存储器技术的风险资本公司Neo Semiconductor将解释“ 3D X-DRAM”,这是一种类似于3D NAND结构的3D 3D技术。 MacRonix国际记忆提供商展示了一种改进的3D DRAM技术,该技术包括两条水平单词线,垂直位线和封闭的晶闸管。能源研究所(SEL)半导体使用半导体氧化物的单片堆积和垂直通道的FET创建了3D原型3D DRAM。 “田间的铁电记忆”,微米技术描述了高性能和长期铁电记忆工程技术。佐治亚理工学院描述了非挥发电容器系统的制造过程铁电冷凝器的小信号的损失。在全局负载捕获的全局内存的内存字段中。 Tsinghua大学展示了与高压CMOS工艺兼容40 nm的3.75 Mbits集成的电阻存储器。

在DRAM部分中,三星是多年来首次回顾DRAM细胞演变的人。在1990年代,平面通道FET是细胞选择晶体管的标准。但是,在21世纪,短渠道和关闭泄漏电流的影响不必要地忽略了。晶体管结构可在不缩短通道的长度的情况下降低横向(水平)方向。持续降低光刻技术可以使DRAM细胞区域持续减少。同时,在2010年的十年中,DRAM细胞基质的设计得到了改进。根据设计规则(或最小加工大小)比较DRAM单元的大小“ F:特征的维度”。通常,最小的单元是2F(垂直尺寸)x 2F(水平尺寸)= 4F2,但这很难实现。在2010年,通过改善DRAM细胞基质的设计,将传统“ 8F2”的细胞区域减少为“ 6f2”。甚至随着相同的处理尺寸,单位面积将减少25%。这种“ 6F2”设计是使用大型DRAM的标准配置。图:在设计“ 6f2”(1990年至2030年代)中,DRAM细胞的演变(1990年至2030年)中,通过嵌入底物中的单词和通道线来减少细胞晶体管区域。水平(水平)源和排水。单元晶体管的垂直结构从基板侧开始,是单词(WL),通道,触点线(BLC),负载存储节点触点(SNC),位点线和细胞冷凝器。单词线空间为2F,位线空间为3F。尽管10 nm(1x和后期)的DRAM细胞基本上基本上保持了先前的结构,但它们继续携带第七代,改善了电容的结构,单词材料材料等,并称为“ 1x→1Y→1Y→1Y→1Y→1Z→1A→1A→1A→1B→1B→1C→1C→1d“能量生成”。但是,下一代低下一代低位(第一个代表” 0a(第一个AS)(第一代“ 0A)”(0A)(“ 0a”(nm)。签名“ 6F2”,并且有一个很好的机会求助于设计“ 4F2”。如何在10 nm以下实现单元格DRAM并实现“ 4F2”设计的基本结构是垂直通道布置的结构。位线,通道(包括侧面的单词线)和电容器垂直从板的侧面进行。图:DRAM细胞基质设计体系结构和垂直通道晶体管的示例。左上方是“ 6f2”设计。晶体管)Samsung(由“ S2CAT:2- self -Anfermitment细胞矩阵晶体管发明”,在右下角,原型细胞基质的Atransvers部分图像在中央通道相对的相对侧观察到了具有电子透射显微镜(TEM)的原型细胞基质(TEM)的能力。这是三星构想和生产的原型。它们被称为“ vs-cat(垂直堆叠细胞基质晶体管)”。左图显示了横截面Of通过电子透射显微镜(TEM)观察到的DRAM细胞基质。在左上角,您会看到3D堆叠的晶体管和电容器,在左下角,您会看到位线提取结构(阶段),在右侧,您会看到单词线和通道的横截面(在两行单词之间插入通道)。右侧的结构图显示了减少硅区域堆叠各种记忆细胞和外围电路的想法。内存细胞(细胞WF)的基质晶片耦合到外围电路晶圆(核/peri.wf)。 3D NAND闪存超过限制。从这里开始,我们将对引言部分的简要说明(以下称为“ flash nand”)。自1990年代中期以来一直在实践的闪光平面记忆经历了密度和微型化的局限性。最初,记忆容量和密度INCRACH主要是由于小型化而导致的,但在2010年代初,小型化已达到极限。这是因为即使有一个被认为是最绝缘干扰的空间,也无法抑制相邻细胞(细胞晶体管)之间最绝缘的干扰,并且细胞可以存储的负载量减少到无法避免干扰的点。图:Evoflash Nand内存(1990年至2030年)当时(打破限制的方法)为3D。基本的NAND Flashlas路由电池链(一系列细胞晶体管)成为垂直的水平。结果,细胞可以存储的负载量显着增加,并且相邻细胞之间的干扰大大减少。此外,使用3D闪存存储器,该公司还成功实现了“多个值的存储”,而传统半导体的内存很难实现。垂直细胞和弦迅速增加密度和通过增加堆叠细胞晶体管的数量来电容。 2010年初的产品有32层。在-2020年代中期,它已增长到300多个水平,约为其原始高度的10倍。此外,在外围电路上方使用了一个设计(矩阵中的CMO)(矩阵中的CMO),从而减少了硅晶圆区域。同时,3D Nand Flash面临着与其前身行星Nand Flash相似的挑战。随着电池的增加,形成细胞链通道的孔变得更深且难以记录。为了缓解这个问题,单词线的细胞晶体管和门(单词线)之间的绝缘膜逐渐变薄。这增加了同一细胞链中相邻细胞之间的干扰,从而减少了可以累积的负载量。此外,构成细胞链通道的孔(存储孔)之间的空间逐渐减小,这有助于提高存储密度。这增加了干扰EEN相邻的细胞链。为了解决这个问题,我们试图用负载陷阱单元的铁电膜代替氮氧化物膜(ONO)作为绝缘门。负载捕获方法确定逻辑值(“高”或“低”位)在能量捕获能量水平上积累负载(主要是执行电子)。铁电膜的逻辑值取决于载荷的方向,而不是通过载荷的方向,而不是通过载荷的方向,而不是通过通过使用降低的编程效果来降低降低的效果。细胞干扰也已证实,“多个存储”可以在细胞水平上兼容。左侧的图像(a)是包含铁电膜(Ferro)的绝缘膜的横向图像。中心(b)是集成到类似于闪光NAND内存的圆柱结构中的铁电膜的横图(TEM)。当阈值电压以16种不同的方式变化(相当于4位/单元)时,右(C)显示了测量结果。三星在他的开幕词中只提到了一些东西。我想找到解决这些问题和其他问题的解决方案。我希望进步继续。越来越多的技术分享演讲,全球的公司和专家分享了很多关于DRAM和NAND的未来的信息。例如,IMEC是第一个呈现纯金属门技术的人。这允许将层间距降低到30 nm,同时保证闪存NAND 3D内存的可靠性。 Kioxia还共享了一种多级编码技术,可以快速随机访问闪存。应用材料已经开发了一种技术来快速发展频道如果在3D NAND中。除3D NAND外,GlobalFoundries还展示了与HKMG CMOS逻辑兼容28 nm的集成闪存技术。他们展示了嵌入34 Mbites的宏闪光的原型。在“ DRAM”领域中,开发3D存储器技术的风险资本公司Neo Semiconductor将解释“ 3D X-DRAM”,这是一种类似于3D NAND结构的3D 3D技术。 MacRonix国际记忆提供商展示了一种改进的3D DRAM技术,该技术包括两条水平单词线,垂直位线和封闭的晶闸管。能源研究所(SEL)半导体使用半导体氧化物的单片堆积和垂直通道的FET创建了3D原型3D DRAM。 “田间的铁电记忆”,微米技术描述了高性能和长期铁电记忆工程技术。佐治亚理工学院描述了非挥发电容器系统的制造过程铁电冷凝器的小信号的损失。在全局负载捕获的全局内存的内存字段中。 Tsinghua大学展示了与高压CMOS工艺兼容40 nm的3.75 Mbits集成的电阻存储器。